FPGAにロジアナコア(BLOGANA)を埋め込む

概要

BLOGANAはブロガナと読みます。Block RAMに入れるLogicAnalyzerという意味です。

BLOGANAでは、以下のことができます。

本マニュアルではBLOGANAの使い方を、簡単なカウンタ回路の内部信号を見ながら説明していきます。FPGAは当社製のARTIX-7ボードを使用します。

サンプルのカウンタ回路

例題として使う回路の仕様は以下の通りとします。

- クロック50MHz

- クロックを分周して、1秒ごとにLED(0)を点滅させる

- 信号"led0_flash"をhighにすると、LED(0)を常時点灯させる

このサンプルコードを示します。 (ファイル名は "main.vhd" とします)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

library UNISIM;

use UNISIM.VComponents.all;

entity main is

Port (

xtalclk_ip : in STD_LOGIC;

led_op : out STD_LOGIC_VECTOR(7 downto 0)

);

end main;

architecture Behavioral of main is

signal clk : std_logic; --50mhz

signal counter : std_logic_vector(31 downto 0);

signal led0_flash : std_logic;

signal led : std_logic_vector(7 downto 0);

begin

clk <= xtalclk_ip;

led_op <= led;

led(0) <= led0_flash;

led(7 downto 1) <= (others => '0');

process (clk)

begin

if clk'event and clk = '1' then

if (counter = conv_std_logic_vector(50000000, 32)) then

counter <= (others => '0');

led0_flash <= not led0_flash;

else

counter <= counter + 1;

end if;

end if;

end process;

end Behavioral;

BLOGANAで内部信号を見る方法

実際に内部の信号をMITOUJTAG上で見るには、まず、VHDLソース中に、以下のようにBLOGANAのコンポーネント宣言とsignalの宣言を行います。

component blogana is

Port ( CLK : in std_logic;

TRIG : in std_logic;

USER_OP : out std_logic_vector(19 downto 0);

SAMPLE_EN : in std_logic;

DIN : in std_logic_vector(71 downto 0);

SAMP_FREQ : in integer range 0 to 2147483647;

WIDTH72 : in std_logic;

LENGTH1024 : in std_logic;

BUSY : out std_logic

);

end component;

signal blogana_din : std_logic_vector(71 downto 0);

signal blogana_trig : std_logic;

signal blogana_width72 : std_logic;

signal blogana_length1024 : std_logic;

signal blogana_busy : std_logic;

signal blogana_user : std_logic_vector(19 downto 0);

コンポーネントの宣言とsignalの定義が終わったら、VHDLソースのbegin以降の場所で、下記のようにbloganaモジュールをインスタンシエートし、下記のように信号を接続します。

inst_blogana : blogana port map

(

clk => clk,

trig => blogana_trig,

din => blogana_din,

USER_OP => blogana_user,

SAMPLE_EN => '1',

samp_freq => 53333333,

width72 => '1',

length1024 => '1',

busy => blogana_busy

);

- SAMPLE_ENは常に'1'、width72とlength1024も'1'にしておいてください。

- clkには、サンプリングしたいクロックを入れてください。

- samp_freqは、そのクロックの周波数をintegerで与えます。

インスタンシエートが終わったら、見たい信号をVHDLのソース中でblogana_dinにつないでいきます。

今回の例では、counter, led0_flash, ledの三つの信号を見たいと思いますので、下記のように接続します。

blogana_din(40) <= led0_flash;

blogana_din(39 downto 32) <= led;

blogana_din(31 downto 0) <= counter;

以上でvhdlの編集は終了です。

編集が終了したらblogana.vhdをプロジェクトに加え、ISEもしくはVivadoで論理合成、配置配線等を行い、bitファイルを生成します。bitファイルの生成が終了したら、MITOUJTAGでbitファイルをFPGAに書き込みます。

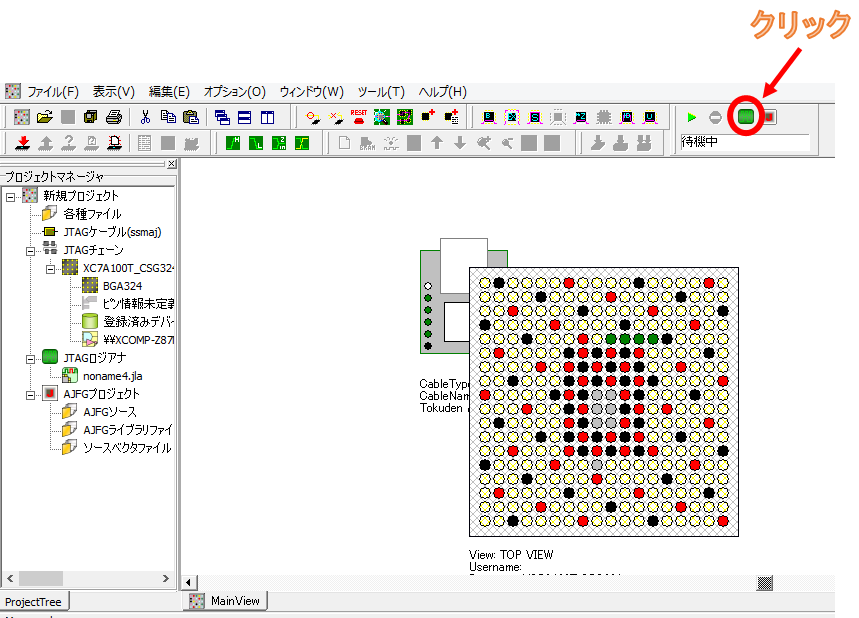

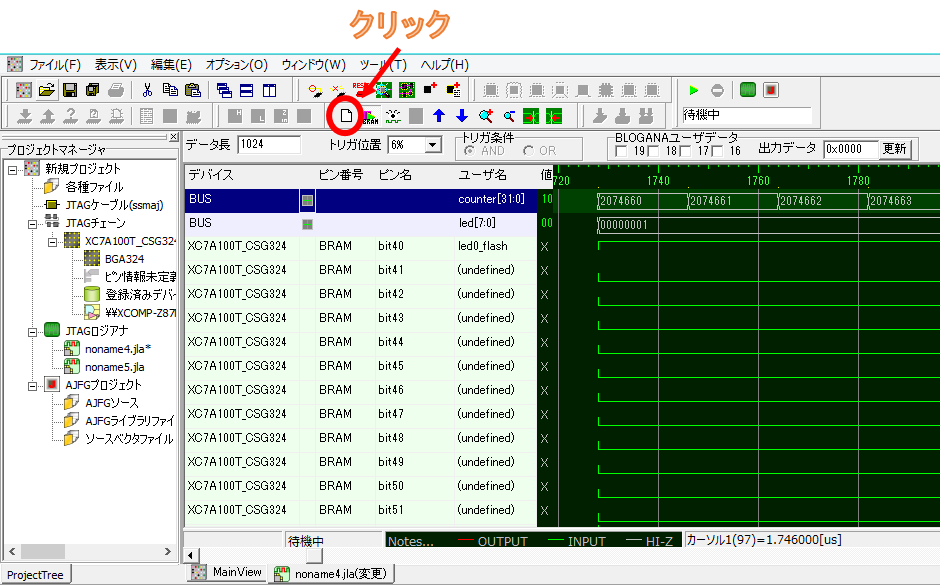

書き込みが終了したら、早速JTAGロジアナを起動します。下図の赤丸印の部分をクリックします。

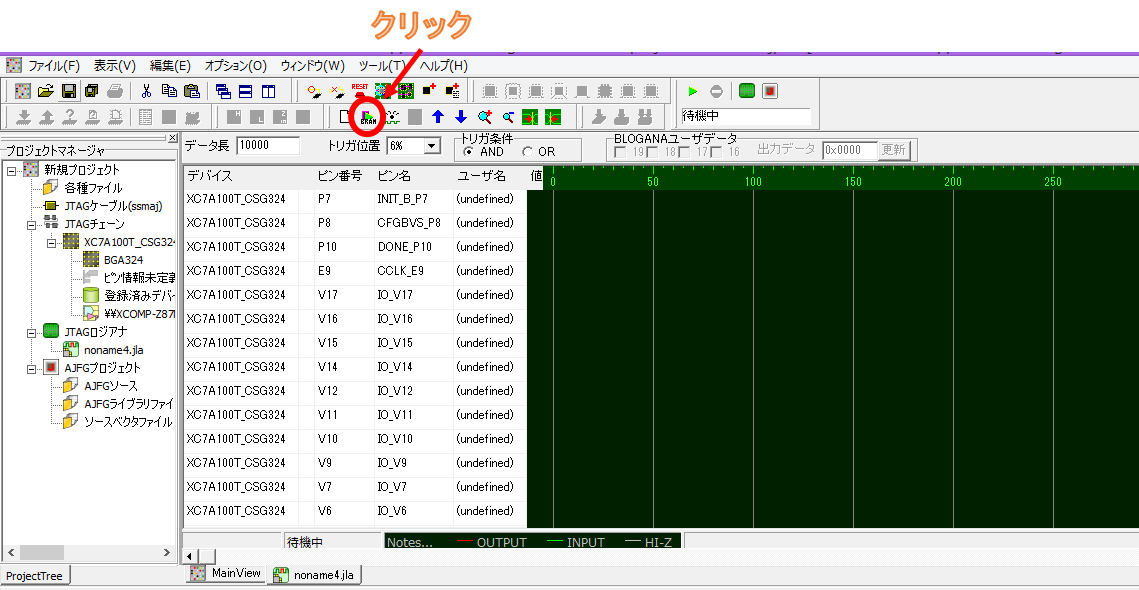

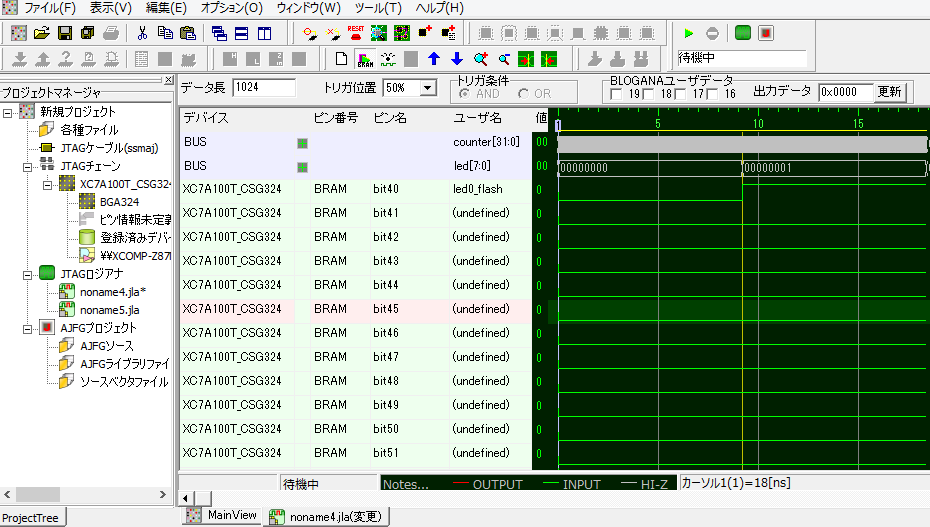

JTAGロジアナが起動したら下図のような画面になります。

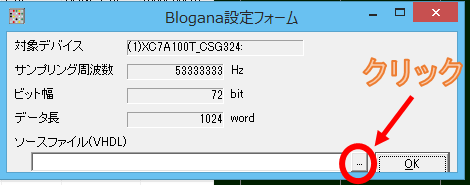

次は、読み込むvhdファイルを選択します。図の赤丸印の部分をクリックします。

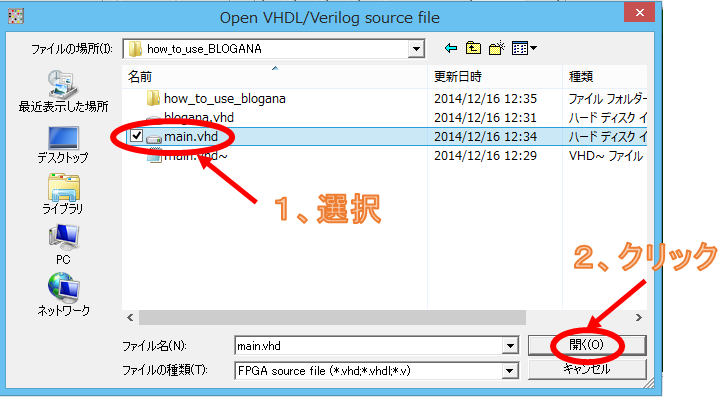

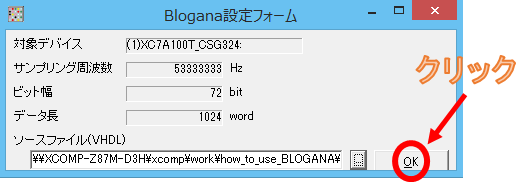

クリックすると下図のようなフォームがでてきます。

図の赤丸印の部分をクリックします。

ここでBLOGANAブロックが記述されているvhdファイルを選択します。

ここではmain.vhdを選択してokをクリックします。

vhdファイルの選択が終了すると、先ほどのフォーム画面のソースファイル部分に選択したファイルのパスが表示されます。確認して合っていれば、okをクリックします。

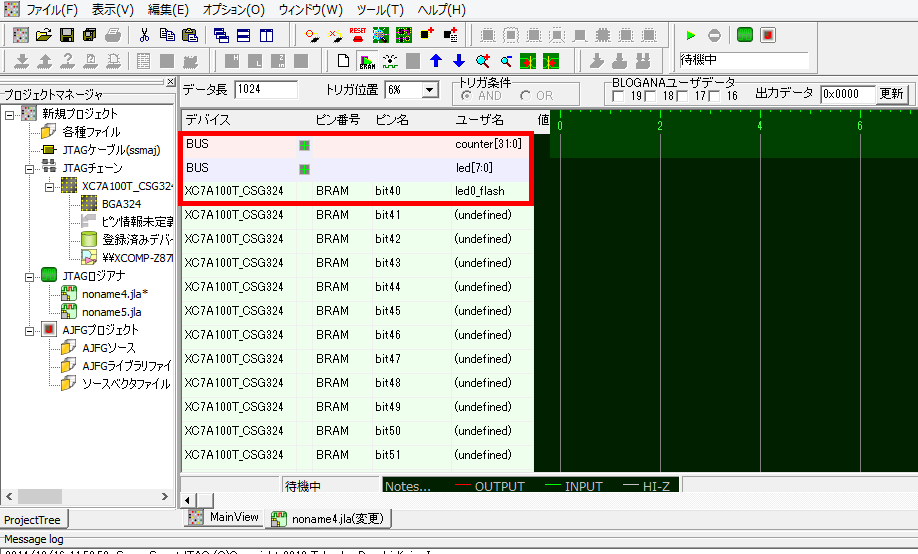

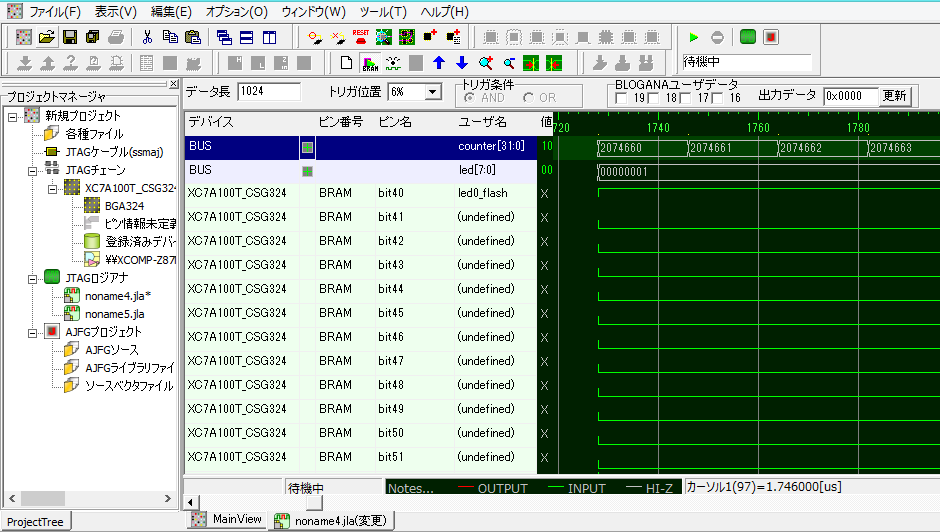

ここまでの操作が完了すると、blogana_dinに接続した信号がMITOUJTAGの画面に表示されます。下図を見ると赤枠の中に先ほど接続したcounter, led, led0_flashが表示されています。BLOGANAではVHDファイルの中身を確認して、最初から自分の定義した信号名で表示してくれるので非常に便利です。

では実際に信号をキャプチャしましょう。

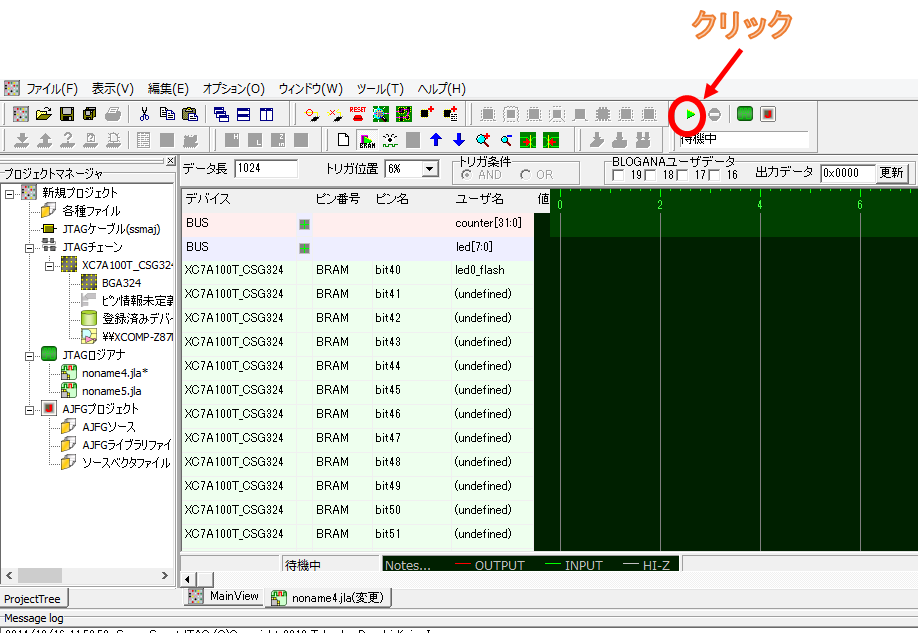

まず下図の再生ボタンをクリックします。

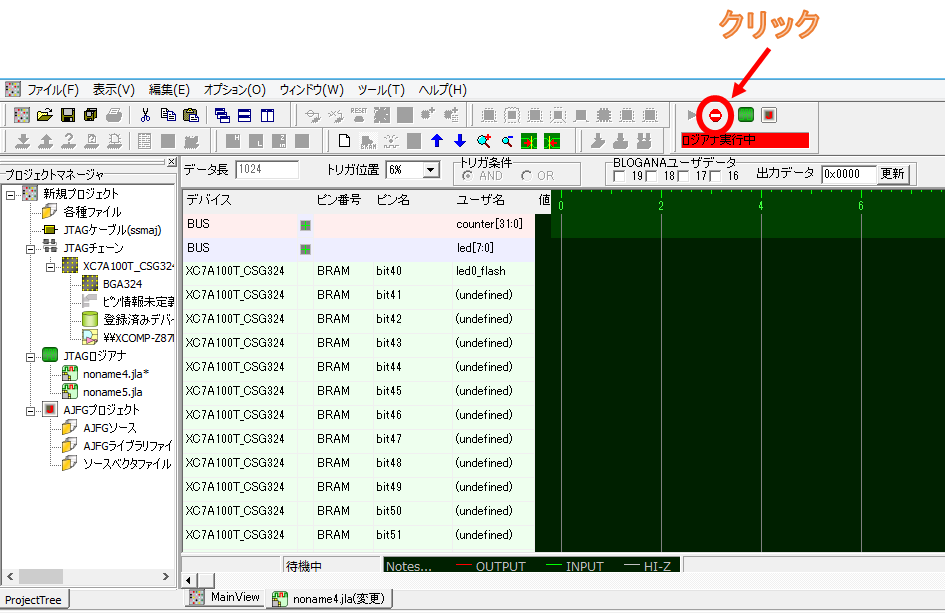

再生ボタンをクリックするとロジアナ実行中になります。ここではトリガーの設定を行っていないので、手動で止める必要があります。止めるときは再生ボタンの右側にある停止ボタンをクリックします。

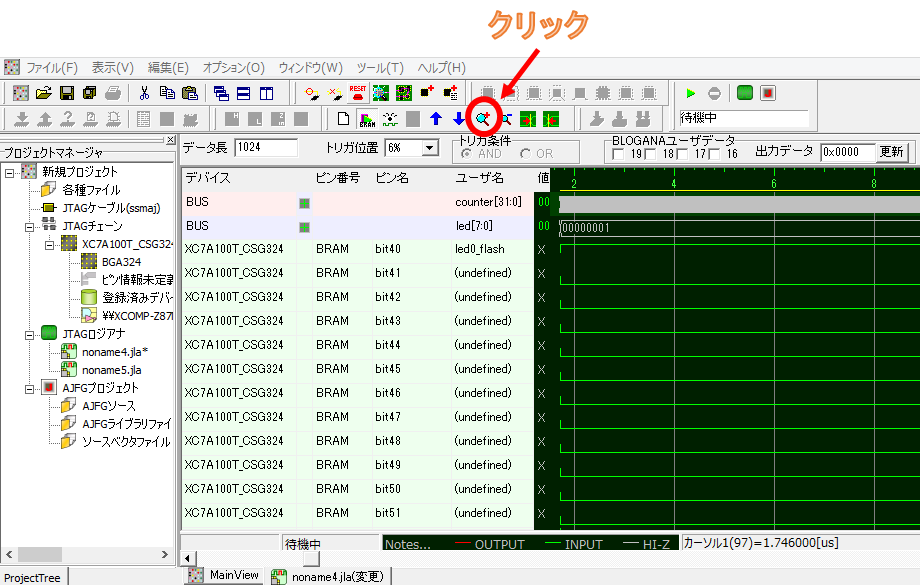

停止ボタンを押すとキャプチャした波形が出力されます。

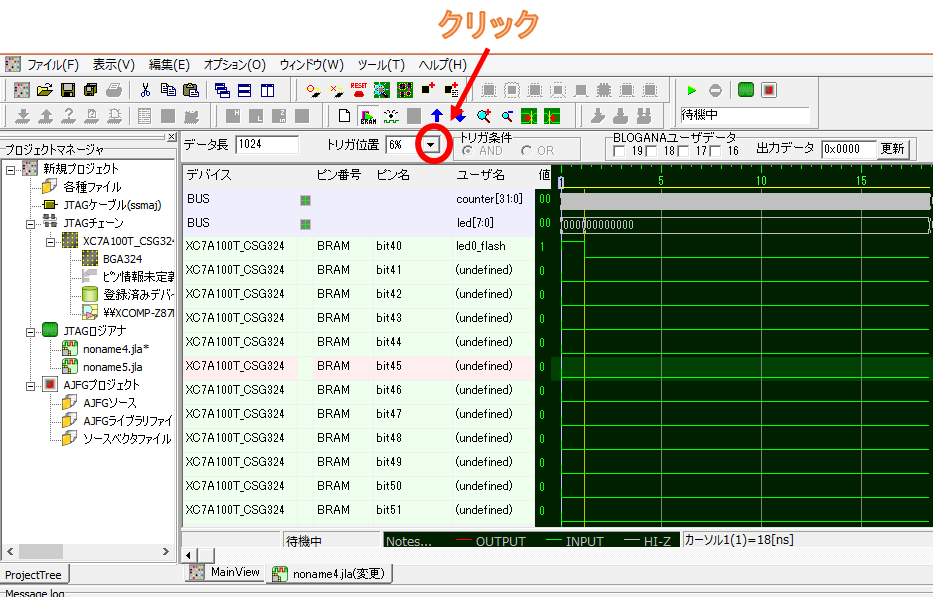

このままではcounterの信号が見にくいので赤丸印の部分を押して拡大していきます。

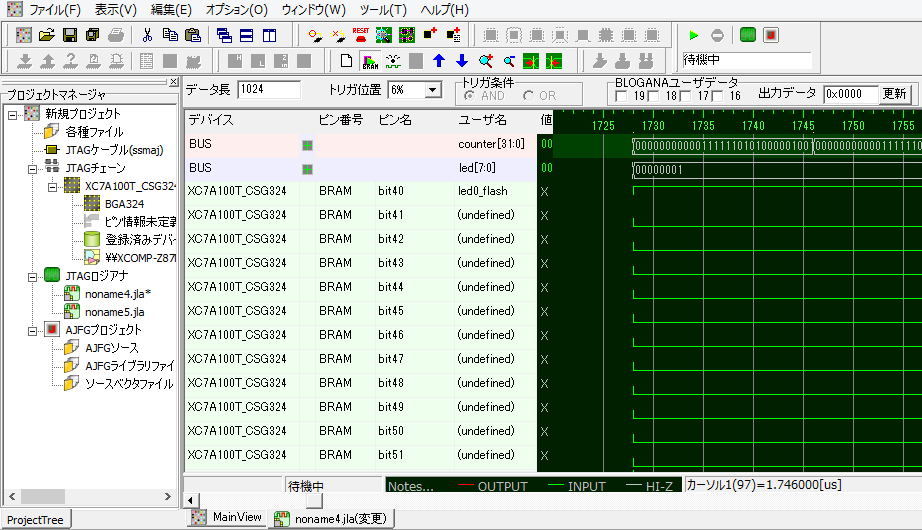

拡大によりcounterの値が見えるようにはなりましたが、二進数表記で読みにくいので十進数表記に変換したいと思います。

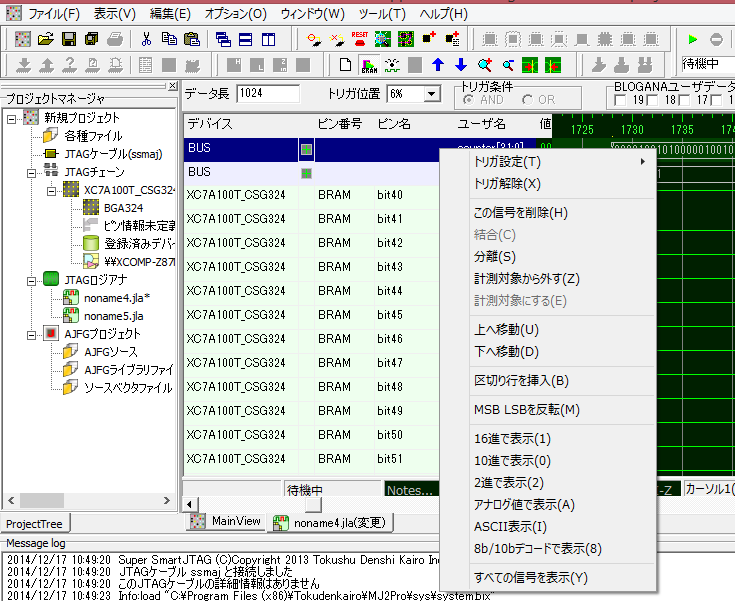

counter部分を左クリックで選択し、その後右クリックして「10進で表示」を選択します。

これでcounterの値が見やすくなりました。counterの値が1ずつ増えているのが見てわかります。またled0_flashは1となっているので、led信号も00000001となっています。次章の「トリガーのかけ方」ではled0_flashの値が変化する前後の信号の状態を見る方法をお伝えしたいと思います。

トリガーのかけ方

本章ではトリガーをかけることで、自分の狙ったタイミングでロジアナの実行を止める手法をお伝えします。

前の章ではロジアナの実行をストップボタンで止めましたが、ロジアナの実行はblogana_trigをアサートしてストップさせることもできます。

ここではled0_flashの値が変化するときにblogana_trigをアサートして波形のキャプチャを行いたいと思います。

したがって以下のような記述をmain.vhdに書き足します。

signal led0_flashd: std_logic;

process (clk)

begin

if clk'event and clk = '1' then

led0_flashd <= led0_flash;

end if;

end process;

blogana_trig <= '1' when led0_flash /= led0_flashd else '0';

vhdlの修正が終わったら再度bitファイルの生成を行い、FPGAにコンフィグレーションします。下図の赤丸部分をクリックしてロジアナデータを初期化したのち、もう一度main.vhdを読み込みます。読み込み完了後、再生ボタンを押しキャプチャを開始します。

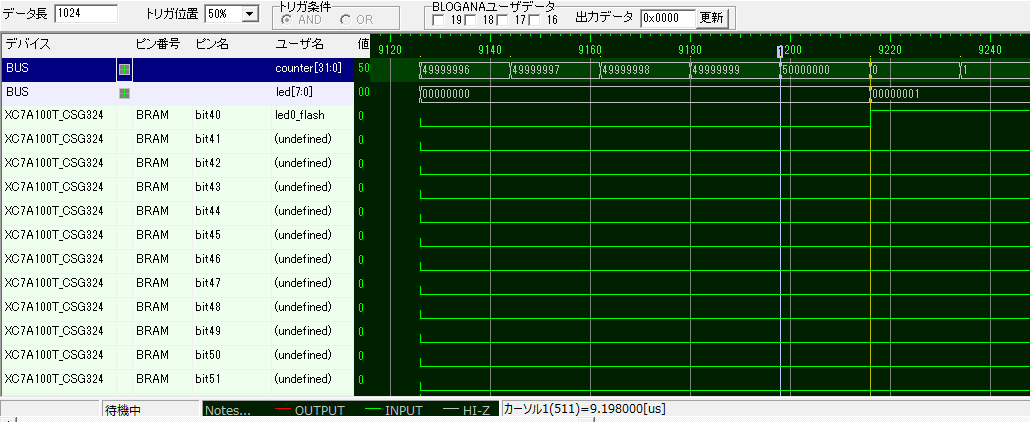

今回はストップボタンを押さなくとも、led0_flashの値が変化したときにキャプチャが自動的に終了します。デフォルトではトリガ位置が6%となっているため、全区間の左から6%の位置でled0_flashの値が変化しています。トリガ位置を50%に変更すると、

下図のように中央部分でled0_flashの値が変化します。

トリガ付近のcounterの値を見ると、counterの値が50000000になったらled0_flashが変化し、counterの値も0に戻っていることがわかります。このようにトリガ機能を使用すると、信号が変化したときの周囲の信号の様子をみることができます。

MITOUJTAGから任意の信号を入力する方法

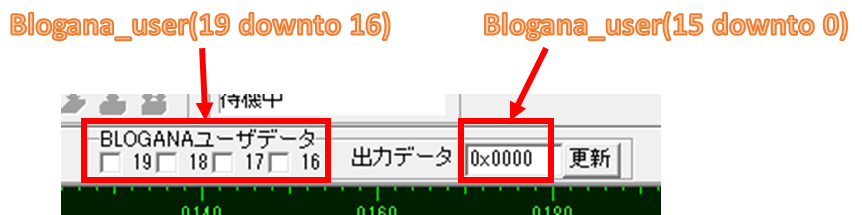

MITOUJTAGのBLOGANAユーザデータ欄に入力した値はblogana_userに出力されます。BLOGANAユーザデータ欄とblogana_userの対応は下図のようになります。

本章ではblogana_userの値を変化させることでcounterの上限を自由に変化できるようにします。まずmain.vhdを以下のように修正します。

if (counter = conv_std_logic_vector(50000000, 32)) then

↓

if (counter = (blogana_user & conv_std_logic_vector(0, 13))) then

bitファイルを生成し、コンフィグレーション等を行います。

その後、下図のようにチェックボックス、出力データを入力して更新ボタンをクリックすると、回路内のblogana_userの値は0x1ffffとなります。この状態で波形をキャプチャしますと、counterの上限値が0x1ffffの下位に13bitの0を加えた値になっていることが分かります。本章ではカウンタの上限値を変更するためにblogana_userを用いましたが、blogana_userの値に応じてトリガの条件を変更させるなどもできます。このような使い方をしますと、デバッグをさらに楽に行うことができます。