簡易接続検査

MITOUJTAGの「簡易接続検査」機能を使うと、基板上のショートや、断線を手軽に発見できます。このチュートリアルでは、簡易接続検査の使い方を説明します。

チュートリアルで使用するボード

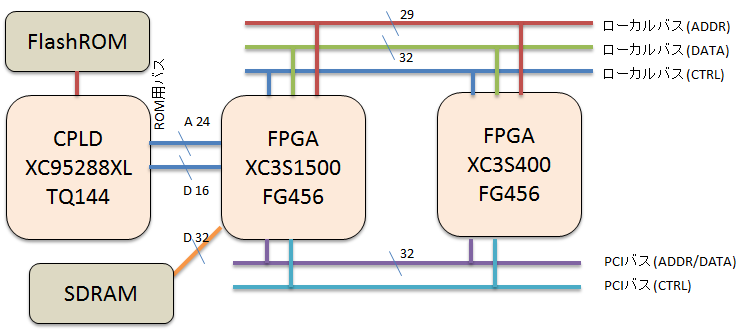

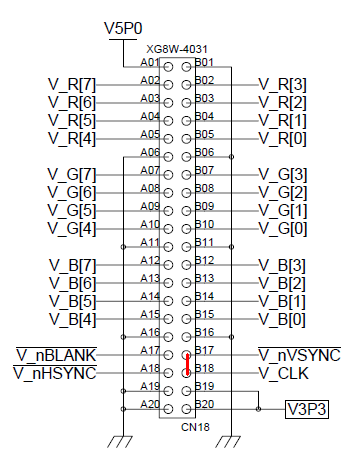

本チュートリアルでは、CQ出版のFPGA評価ボード「BLANCA」を用います。

BLANCAは、右上の図のように、2つのFPGAとCPLD間を非常に多くの配線でつないでいるため、このような接続検査の例題として最適だからです。

基板検査に入る前の準備

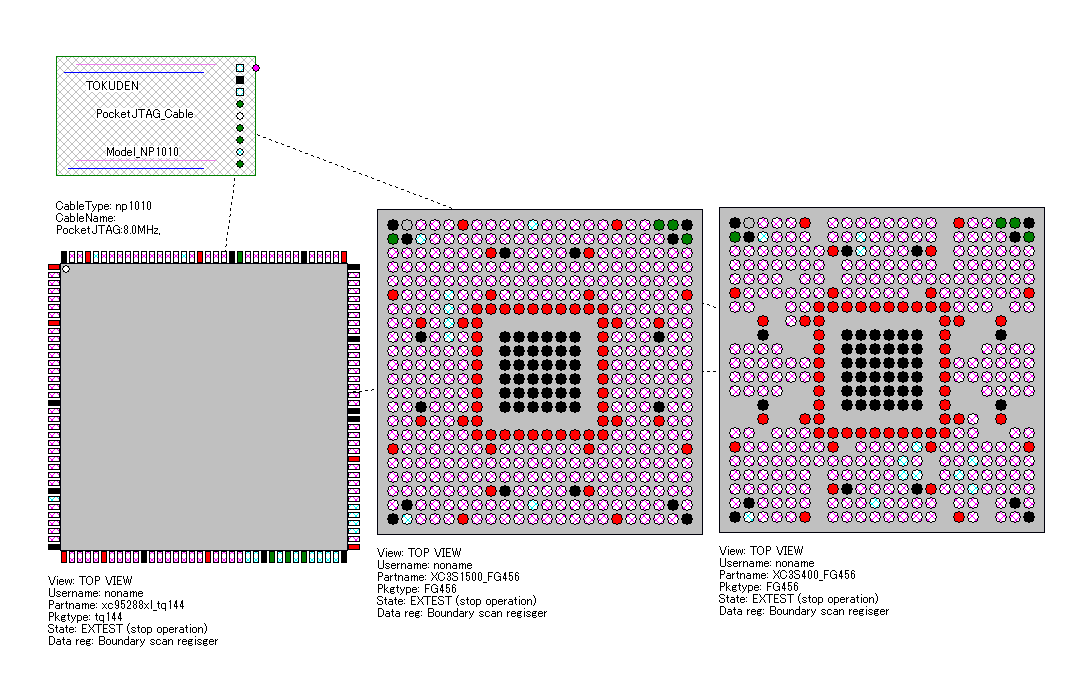

MITOUJTAGを起動し、ターゲットボードと接続します。そして、デバイスを自動認識してバウンダリスキャンで端子が見えることを確認しておきます。

FPGAは未コンフィグ状態にすること

この検査を行うとき、FPGAは未コンフィグの状態にしなければなりません。なぜならば、FPGAはコンフィギュレーションされて動き出すと、I/Oの方向がJTAGで操作できない場合があるからです。未コンフィギュレーション状態のFPGAの端子はバウンダリスキャンで入力にも出力にも設定できますが、コンフィグされたFPGAでは、その端子がOUTOUT専用で作られた場合、JTAGでもINPUTにできない場合があります。(その逆もある)

ピン定義ファイルを読み込んでおくこと

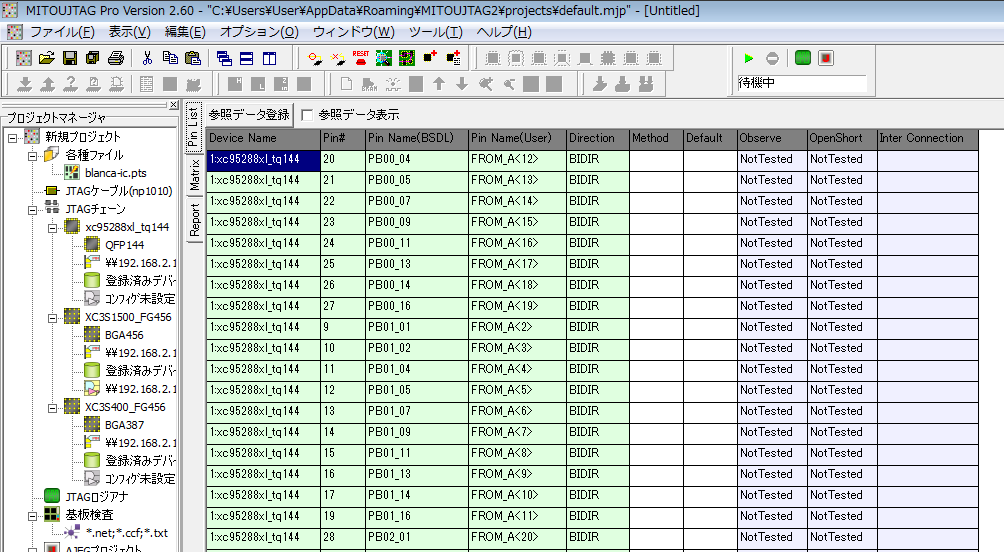

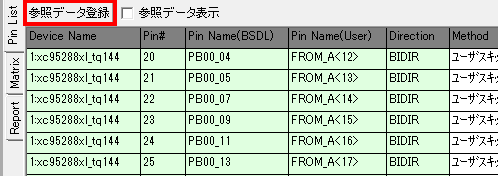

検査をスムーズに行うコツは、ターゲットボード上のFPGAにはあらかじめピンファイルを読み込んでおくことです。そうすることで、異常が見つかったピンの名前がわかるので、異常を探しやすくなります。

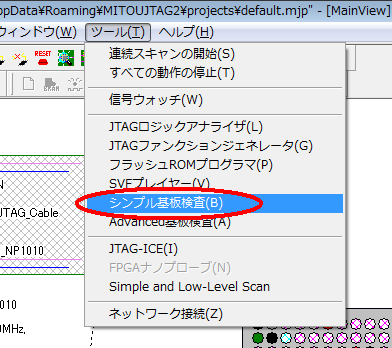

簡易接続検査ツールの起動

簡易接続検査ツールを起動するには、MITOUJTAGのメインメニューから「ツール→簡易接続検査」を選びます。バージョンによっては「シンプル基板検査」と表示されている場合もあります。

簡易接続検査ツールを起動するには、MITOUJTAGのメインメニューから「ツール→簡易接続検査」を選びます。バージョンによっては「シンプル基板検査」と表示されている場合もあります。

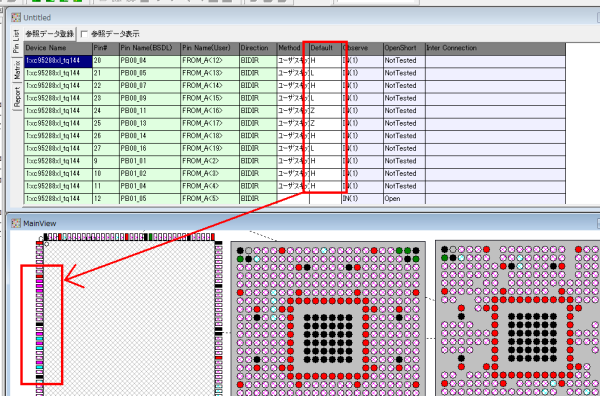

起動すると、次の図のような画面が表示されます。

検査における注意事項

デフォルトの検査では、すべてのピンを順番にH→Z→L→Zと動かし、そのパターンが他のどこかのピンから検出されるかを調べて、接続を判断しています。注意すべき点は、すべての端子を検査してしまうことです。

電源の制御信号や、モーターの制御信号など、不用意に操作してはいけない端子であっても検査してしまうので、危険な端子は検査しないように除外しなければなりません。除外の方法は本ページの後ろの節で紹介します。

検査の実行

ここで、ツールバーのスタートボタンを押せば、全ピンの検査が開始します。

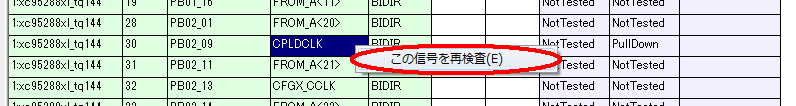

特定の行を右クリックして、「この行を再検査」を行うと、その信号だけを検査できます。

検査結果の読み方

例えば、次の図のような検査結果となったとします。この場合の読み方を説明します。

検査結果は表の中の青いセルに表示されます。

(1)Observeセルの見方

最初の列のIN(1)というのは、検査前に端子の状態を調べたところIN方向になっていてロジックレベルが1であったことを示しています。

Toggleと表示された場合は、その信号がトグルしていることを示します。例えばクロック入力などが入ってきている場合はToggleになります。Toggleとなった場合は、オープンショートテストやインターコネクトテストは行われません。

(2)OpenShortセルの見方

次のセルは、その端子が単体でどのような構造をしているかを示しています。

- PullUp ・・・ プルアップされています

- PullDown ・・・ プルダウンされています

- Open ・・・どこにもつながっていないオープンな端子と考えられます

- LOW ・・・ 強力にLに引かれています。GNDとショートしている可能性が高いです。

- HIGH ・・・ 強力にHに引かれています。VCCとショートしている可能性が高いです。

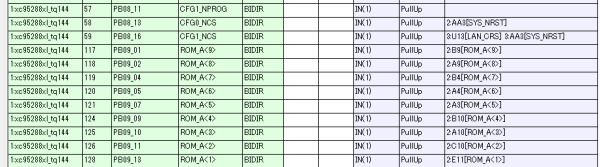

(3) InterConnectionセルの見方

その端子が接続されていると思われる先の端子名が表示されます。

例えば、2:A4[ROM_A<6>]となっていた場合、JTAGの2番目のICのA4番端子につながっているということを示しています。ROM_A<6>はピン定義ファイルから読み込んだピン名です。

複数の端子につながっていると判断された場合は、3:U3[LAN_CRS] 3:AA3[SYS_NRST]のように複数の信号が並べて表示されます。

検査を安全に行うためのカスタマイズ

検査から除外する端子を設定する方法

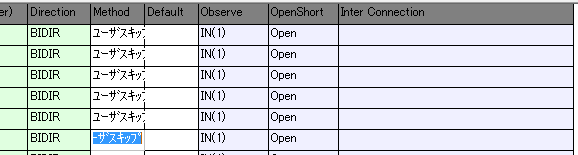

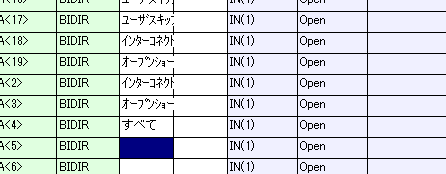

この検査はデフォルトではすべての端子に対して行われてしまうので、使い方を間違えると危険です。検査してはいけない端子を除外するには、Methodと書かれた列のセルに「S」を入力します。※Sと入力すると、自動的にユーザスキップと変わる。

ユーザスキップに設定された端子は、オープンショートテストとインターコネクトテストの両方が行われません。(端子の観測のみ行われます)

オープンショート、またはインターコネクトのどちらか一方を実行する方法

Methodの列に「I」と入力するとインターコネクトテストのみ行われます。

Methodの列に「O」と入力するとオープンショートテストのみ行われます。

Methodの列に「A」と入力すると両方のテストが行われます。(※デフォルトと同じ)

- インターコネクトテスト・・・接続先を調べる

- オープンショートテスト・・・端子がオープンなのか、プルアップ等なのかを調べる

検査中の出力状態の設定

検査をしている待機中、すべてのピンはZ(ハイインピーダンス・入力)状態になっています。しかしながら、モーターなどを動かすピンや他のICのリセットピンでは特定の値に固定しておかなければならないことがあります。

そのような場合、Defaultと書かれたセルにHまたはLと書いておくことで、検査待機中の状態を固定することができます。

参照データの登録と比較

正常に動作する基板でデータを取得したら、「参照データ登録」と書かれたボタンを押します。

これで、オープンショートの結果や、接続先の結果が登録されます。参照データを見たい場合は、「参照データ表示」と書かれたチェックボックスをONにしてください。

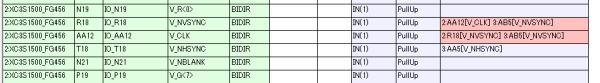

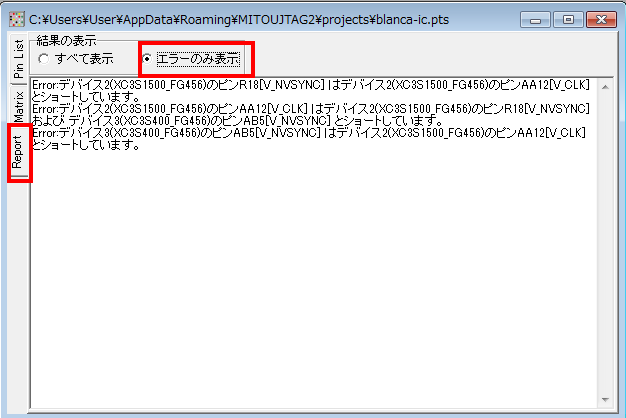

ためしに、この基板のコネクタ上でV_nVSYNCという信号とV_CLKという信号をショートさせたところ、

上の図のように、V_NVSYNCとV_CLKという信号が、参照データと異なるため赤い色で表示されました。

また、エラーレポート表示(Reportタブをクリックし、エラーのみ表示をチェックする)と、問題のある信号の状態のみピックアップされて表示されます。

まとめ

簡易接続検査を行う場合のポイントは以下のとおりです。

- FPGAは未コンフィグ状態にする。CPUはリセットをかけておく。

- FPGAの場合は、ピン定義ファイルを読み込んでおく(わかりやすくなるため)

- 検査してはいけないピンはSKIPを指定する

事前準備なしでいきなり検査しても、基板上でショートしているのがわかるのでかなり便利だと思います。