CPLDを実機デバッグする

CPLDは埋め込みJTAGロジックアナライザが使えない

各社から、FPGAデバッグツールとして、IPコアを埋め込むタイプのJTAGロジックアナライザがリリースされていますが、それらはCPLDに対して使うことができません。

なぜならば、CPLDは内蔵メモリを持っていないため、波形を蓄えることができないからです。したがって、各社がリリースしているFPGAデバッグツールはCPLDに対しては一切使うことができず、CPLDを実機でデバッグするには、JTAGバウンダリスキャンを行う以外の選択肢はないのです。だから、MITOUJTAGは、CPLDに対する唯一のデバッグ手段となります。

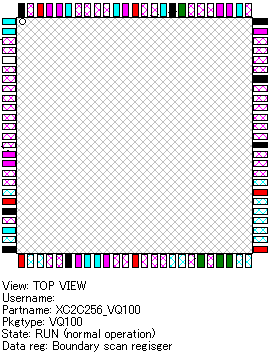

CPLDの端子の状態を見る

CPLDは規模が小さいため軽視されがちですが、回路の重要な一翼を担っているのは言うまでもありません。MITOUJTAGを使うと、CPLDの端子さえも可視化することができます。

下の図のように、CPLDの端子のH/L、入力/出力の区別を色分けと塗り分けによって表示します。

図1 CoolRunner2の端子の状態を可視化

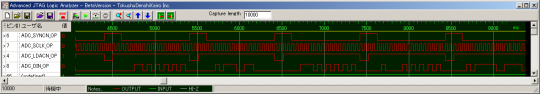

CPLDの端子の状態を波形で見る

シリアルDACを操作してDCオフセットを与える場合など、動作速度を落としても問題ないアプリケーションでは、クロックを十分に落とすことでバウンダリスキャンで端子の状態が読めるようになります。

例えば、50MHzで動く回路を100Hzくらいで動かすようにすれば、バウンダリスキャンを用いたロジックアナライザでも、信号の遷移を取りのがすことなくキャプチャすることができるでしょう。

図1 CoolRunner2の端子の状態

CPLDは、FPGAとは違い電源ONで即スタートする部品です。

FPGAやCPUの安定起動のために重要な処理を行っている可能性もあります。規模が小さいからといって軽視することなく、JTAGを使って十分なデバッグを心がけたいものです。