フラッシュROM

フラッシュROMの読み書き

平成16年11月2日

MITOUJTAG version 0.2以降では、JTAGフラッシュROMライターが内蔵されています。このチュートリアルでは、MITOUJTAGに内蔵されたフラッシュROMライターの操作方法を解説します。このフラッシュROMライターは、任意のFPGAやCPUと、任意の配線方法で接続されたフラッシュROMにアクセスすることができます。

原理

フラッシュROMは一般的にはJTAGに対応したデバイスではないので、フラッシュROMに接続されたJTAG対応デバイスの入出力端子を操作して、間接的にアクセスします。

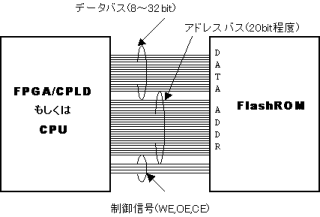

組み込みシステムにおいて、フラッシュROMは図1のようにFPGAやCPUの入出力端子に接続されています。これは、複数のデバイスに接続されることもありますが、基本的にはフラッシュROMの信号は、何らかのデバイスのIOに接続されていると考えられます。

図1 フラッシュROMの一般的な接続

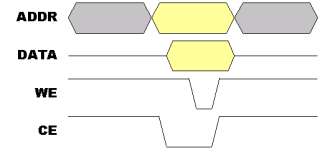

フラッシュROMの内容を読み書きするためには、図2のように、フラッシュROMのアドレスバスやデータバスに値を設定し、CEやWE、OEなどの制御信号を操作することで行います。

図2 フラッシュROMアクセスの例

?

以上のように、フラッシュROMの読み書きはスタティックRAMと同様の方法でアクセスできます。

JTAGを使ってフラッシュROMを読み書きするためには、バウンダリスキャンを用いて図1のFPGAやCPLDまたはCPUの入出力を操作し、アドレスバスやデータバスに必要なデータを載せ、WEやCEにLのパルスを作り出すことによって行います。1ワードの書き込みを行うためには、何回か入出力の状態を更新しなければならないので、複数回のバウンダリスキャンを行うことになります。

また、フラッシュROMでは上記でいうところの書き込みを行った場合、スタティックRAMのようにそのアドレスで示されたメモリのセルに書き込まれるわけではありません。フラッシュROMでは、アドレスとデータバスは合わせて「コマンド」として解釈されます。特定のアドレスとデータの組み合わせの書き込み操作を行うことにより、消去や書き込み、さらには書き込みプロテクトなどの複雑なコマンドが実行される仕組みになっています。

フラッシュROMライタの起動

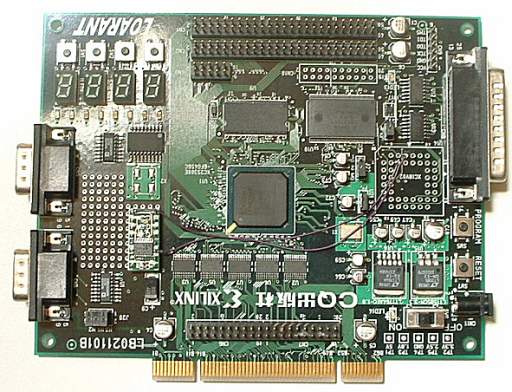

ここでは、CQ出版のSpartanIIE評価ボード(XC2S300E)を例に、フラッシュROMライタの操作方法を解説します。このボードでは、FPGAはXC2S300Eを、フラッシュROMは富士通の29PL3200TEを使用しており、FPGAとROMは32ビットのバスで接続されています。

写真1 CQ出版 SpartanIIE評価ボード

?

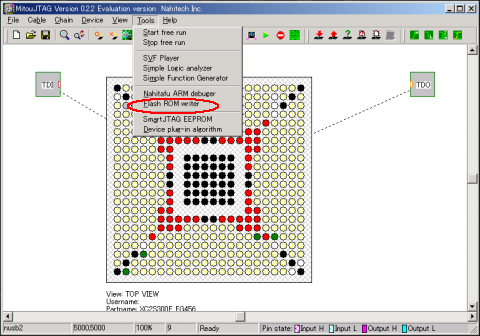

MITOUJTAGを起動したら、フラッシュROMに接続されているJTAG対応デバイスを自動認識あるいは手動で追加します。

図3 フラッシュROMに接続しているデバイスを認識

メインメニューのToolsから、Flash ROM writerを起動します。

ピン割り当ての設定

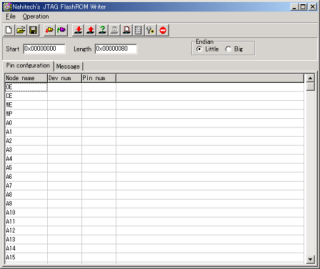

Flash ROM Writeを起動すると、図4のようなウィンドウが開きます。この画面ではフラッシュROMの各信号とそれを操作するJTAG対応デバイスのピン番号(あるいはUCFファイルで定義されたピン名)を入力します。

このSpartanIIE評価ボードでは、フラッシュROMのA0の信号は、FPGAのP21番ピン※に接続されています。このような場合、図4の画面で「Node name」には「A0」と入力し、「Dev num」には「1」と入力し、「Pin num」には「P21」と入力します。

※XC2S300EFG456はBGAなので、21番ピンではなく、P21番ピンである。

「Node name」の欄には、アドレスバスはA0やA16のように記述し、データバスはD0やD15のように数字を併記します。また、データリード制御信号はOEと記述し、データライト制御信号はWEと記述し、チップイネーブルはCEと記述します。ライトプロテクト端子がある場合はWPと記述します。

表1 ピン設定の表記

|

機能 |

記述 |

|---|---|

|

データ |

D? |

|

アドレス |

A? |

|

書き込み制御 |

WR |

|

読み出し制御 |

OE |

|

チップイネーブル |

CE |

|

ライトプロテクト |

WP |

|

常に1にする端子 |

PULLUP |

|

常に0にする端子 |

PULLDOWN |

|

ハイインピーダンスにする端子 |

HIGHZ |

?

常に1や0にする端子とは、フラッシュROMの追加機能の制御線(バイト/ワード選択等)や、FPGAに接続されている他のデバイスに与える信号です。例えば、FPGAにLANコントローラが接続されているような場合では、フラッシュROM書き込み中にLANコントローラが動作してしまわないよう、ディゼーブルにするために用います。HIGHZも同様に、FPGAにつながった他のデバイスが出力している信号と衝突しないようにするために用います。

これらのピン割り当ての定義を行うと、前述のSpartanIIE評価ボードでは、次のファイルのようになります。ピン定義の参考例としてご利用ください。

-

cq-xc2s300e.jfc?(CQ出版SpartanIIE評価ボード用 フラッシュROM定義ファイル)

ピン割り当ての定義は、ファイルに保存しておくことができます。この際、ファイルの拡張子はJFC (JTAG Flash Configurationの略)となります。

操作

ピン割り当てを設定したら、次の表を参照して、行いたい操作のボタンを押します。

表2 各アイコンとその機能

|

画面上の表示 |

機能 |

|---|---|

|

|

ピン定義を初期化する |

|

|

ピン定義ファイルを読み込む |

|

|

ピン定義をファイルに保存する |

|

|

フラッシュROMにファイルから書き込む |

|

|

フラッシュROMから読み出し、ファイルに保存する |

|

|

フラッシュROMの内容とファイルの内容を比較する |

|

|

フラッシュROMを全消去する |

|

|

フラッシュROMをダンプする |

|

|

フラッシュROMのCFIコードを読み出す |

|

|

現在の操作を停止する |

|

|

操作を開始するアドレスを指定する |

|

|

操作する長さを指定する |

|

|

エンディアンを指定する |

?

Startアドレスや、長さはすべてワード単位で設定します。例えば、65536バイトのファイルを書き込みたい場合、フラッシュROMとFPGAのデータバスの接続が16ビットである場合、Lengthには0x10000ではなく、0x8000と指定します。

?

あとは、フラッシュROMに自由自在にアクセスすることができます。

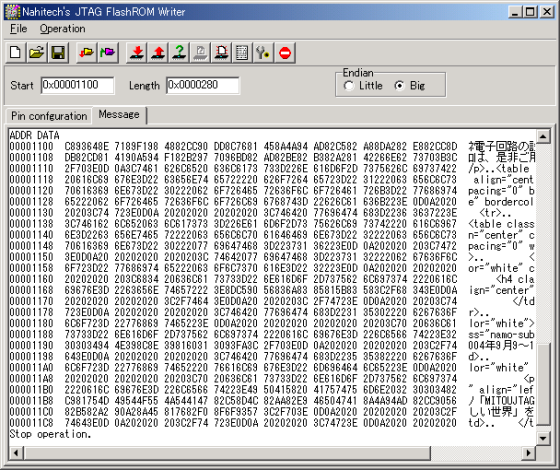

図5 フラッシュROMに書き込んだデータをダンプしている様子

?

活用方法

このフラッシュROMライタは、バウンダリスキャンで全端子を操作するため、速度的にはあまり速くはありません。したがって、CPU上で動作するモニタプログラムや、FPGA上の回路から書き込みができる場合はそちらを利用したほうが高速です。

しかしながら、FPGAのコンフィギュレーションデータがフラッシュROM上にあるようなボードや、CPUのモニタプログラムがフラッシュROMに入っている場合、フラッシュROMが消えるとにっちもさっちもどうにもいかなくなってしまうことがあります。そのような場合には、このJTAGフラッシュROMライターが役に立ちます。

?

表3 フラッシュROM書き込み速度の実績

|

対象ボード |

デバイス |

書き込み時間 |

読み出し時間 |

|---|---|---|---|

|

CQ評価ボードSpartanIIE |

XC2S300EFG456 |

104Bytes/秒 |

303Bytes/秒 |

|

SUZAKU |

XC3S400FG256 29DL32TF 16ビット幅で接続 |

77Bytes/秒 |

226Bytes/秒 |

?

XC2S300Eの方がXC3S400よりもバウンダリスキャンレジスタ長が長いので、1ワードの書き込みはSUZAKUの方が速くなります。しかし、SUZAKUはフラッシュROMとFPGAを16ビット幅※で接続するのに対し、CQ評価ボードは32ビット幅で接続するので1ワードあたり2倍のサイズの書き込みができます。結局、SUZAKUよりもCQ評価ボードの方が約1.3倍高速に読み書きができています。

※本来、SUZAKUのFPGAとフラッシュROMは8ビットで接続するのが正当な方法であるが、この実験では上手く16ビットで接続できた。

?

フラッシュROM全域を書き換えると約半日~1日かかるので、デバイスプログラミングとして使うととても遅いのですが、組み込みシステムの開発時にブートローダを書き込む用途やBIOSが消えてしまった場合などの救済策としてはとても有効です。

MITOUJTAG Version0.2における制約

-

バス幅が8/16ビットなど複数選べる場合は、必ず広い方をご採用ください。

-

このフラッシュROMプログラマは、AMD/富士通系のフラッシュROMのみ対応しています。