基本的な操作方法

MITOUJTAGの基本的な操作方法

このチュートリアルでは、MITOUJTAGを使って、FPGA用コンフィギュレーションROMにプログラミングする方法と、バウンダリスキャンを実践する方法を説明します。

このチュートリアルでは、「NP1003E」というFPGA評価ボードを使用します。実際にMITOUJTAGをお使いになる場合は、お客様ご使用のボードにあわせて、読み替えてください。

ハードウェアのセットアップ

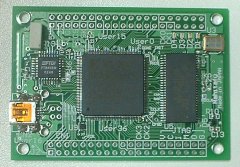

NP1003Eには、コンフィグROM(XCF01)とFPGA(Spartan2-100)が搭載されています。

NP1003Eには、コンフィグROM(XCF01)とFPGA(Spartan2-100)が搭載されています。

?

?

?

?

?

FPGAボードのJTAG信号、TCK、TDI、TMS、TDO、そして電源のVCCとGNDをJTAGケーブルに接続します。JTAGケーブルは、XILINX Parallel III互換のものです。ケーブル内には、74HC125のバッファがあるため、VCCも接続する必要があります。

FPGAボードのJTAG信号、TCK、TDI、TMS、TDO、そして電源のVCCとGNDをJTAGケーブルに接続します。JTAGケーブルは、XILINX Parallel III互換のものです。ケーブル内には、74HC125のバッファがあるため、VCCも接続する必要があります。

JTAGケーブルを接続したら、FPGAボードの電源を投入(USBケーブルを接続する)します。

ソフトウェアの起動からケーブルの接続まで

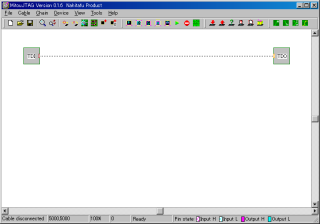

MITOUJTAGを起動します。

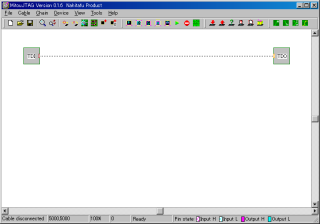

TDIとTDOと書かれた灰色の四角が表示されており、起動直後にはデバイスは何も表示されていません。

MITOUJTAGの起動後に最初に行う作業は、「ケーブルの選択」です。ケーブルを選択するには、下の図に示したように、メインメニューの丸印の書かれたツールバーのボタンを押すか、メインメニューから「Cable→Connect」を実行します。

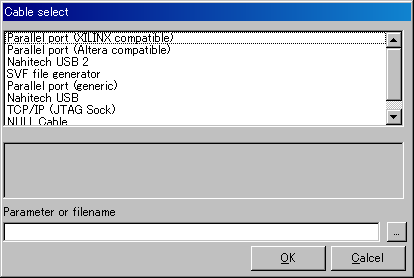

すると、次の図のようなダイアログが開きます。

このダイアログでは、使用しているJTAGケーブルの種類を選択します。今回はXILINXのParallel cable III互換のケーブルを使用しているため、一番上の「Parallel port (XILINX compatible)」を選択します。

ALTERA互換のケーブルを使用している場合は、「Parallel port (ALTERA compatible)」を選択してください。

?

使用するケーブルの部分をダブルクリックするか、シングルクリックで選択した後、OKボタンを押します。

すると、MITOUJTAGの画面の左下にprnprtと表示され、プリンタポート経由でJTAGに接続していることがわかります。

デバイスの自動認識とパッケージの選択

ケーブル接続に行う作業は、「デバイスの追加」です。

デバイスの追加は、MITOUJTAGのメイン画面から行います。

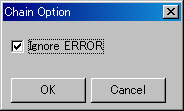

下の図に示したような虫眼鏡の描かれたツールバーのボタンを押すか、メインメニューから「Chain→Detect」を実行します。

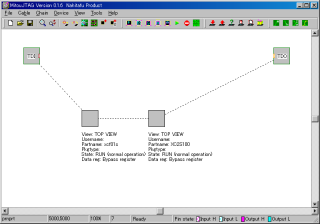

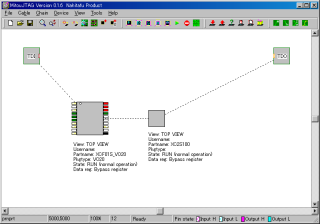

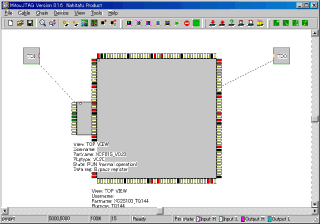

すると、下の図のように、2つのデバイスが認識されます。

(※ 実際に認識されるデバイスの数と種類は、ご使用のボードによって変わります。)

?

もし、デバイスが認識されない場合は、次の原因が考えられます。

-

JTAGケーブルやプリンタポートが接触不良をおこしている。

-

ターゲット基板の電源が入っていない。

-

ターゲットデバイスがJTAGに対応していないか、JTAGが使用できないモードになっている。

-

ターゲットデバイスがJTAGのIDCODEを実装していない。

-

ターゲットデバイスがJTAG規格(IEEE1149.1)を正しく実装していない。

※ JTAG対応のCPUでは、JTAGが正しく実装されていないことがよくあります。

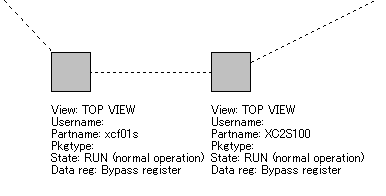

上の図のように、2つの灰色の四角が表示されたら、灰色の四角の下に書かれている文字を読んでください。

左側の四角は、Partname:xcf01sと書かれていて、右側の四角は、Partname:XC2S100と書かれています。

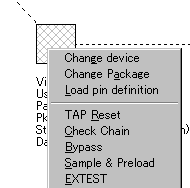

ここで、左側の灰色の四角の上にマウスカーソルを移動し、右クリックをしてください。プルダウンメニューが表れるので、Change deviceを選択します。

ここで、左側の灰色の四角の上にマウスカーソルを移動し、右クリックをしてください。プルダウンメニューが表れるので、Change deviceを選択します。

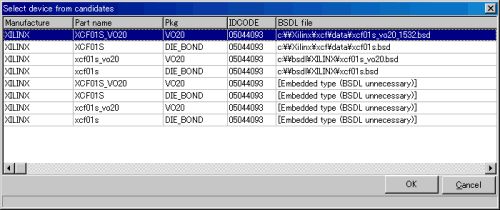

次の図のようなダイアログが表示されます。このダイアログは同じIDCODEを持つデバイスの一覧が表示されているので、ご使用のデバイスに最も適した

パッケージを持つデバイスを選択してください。

?

NP1003で使用しているパッケージのタイプはXCF01SVO20なので、一番上に表示されたVO20のものを選びます。同じパッケージの候補が複数ある場合はどれを選んでも構いません。

これで、左側のデバイス(XCF01S)のパッケージが表示されました。

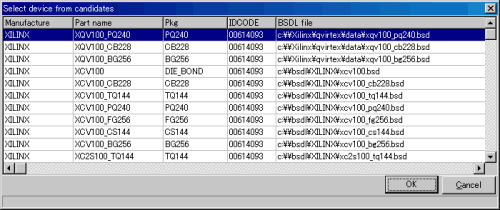

同様に右側のデバイスも同じようにChange deviceを実行して、パッケージを選択してください。

今度は、候補がいろいろと出てきます。

中には、XCV100というVirtexも表示されていますが、Spratan2とVirtexはIDCODEが重なっているため、SpartanIIと同時にVirtexも表示されます。

デバイスの候補一覧の中からXC2S100_TQ144と書かれたデバイスを探し、OKボタンを押します。

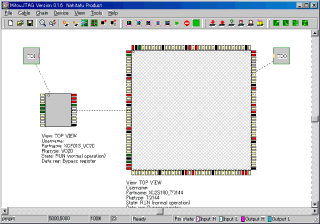

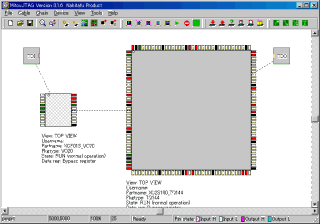

すると、下の図のようにSpratan2のTQ144ピンのものが表示されます。

デバイスが重なって見にくい場合は、Spartan2のパッケージ部分(灰色のところ)にマウスカーソルを合わせ、左クリックでドラッグし、適当な位置に移動します。

これで、デバイスの認識とパッケージの選択は終了です。

FPGA用データファイルの作成

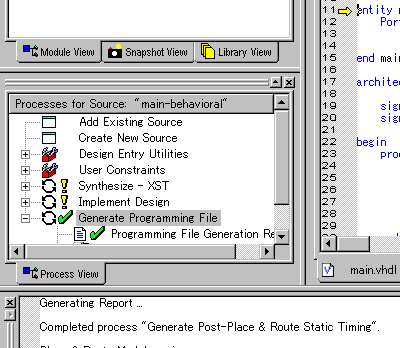

XILINXのISE Foundationや、ISE WebPACKを用いて、デザインをコンパイル(Synthesize & Imprement & Generate Programming File)します。

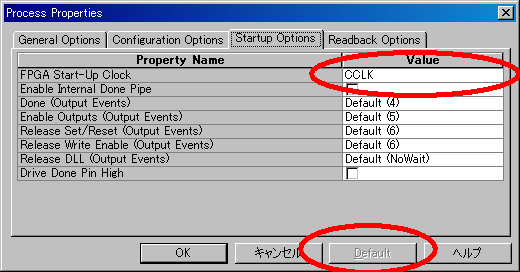

このとき、Generate Programming Fileのオプションで、Start-UP Clockの設定がCCLKになっていることを確認してください。

Start-UPオプションは、以下の条件で使い分けます。

-

CCLK ・・・ コンフィグROMに書き込む場合

-

JTAGCLK ・・・ FPGAに直接JTAGコンフィギュレーションを行う場合。

本チュートリアルでは、コンフィグROMに書き込むため、CCLKを選択します。

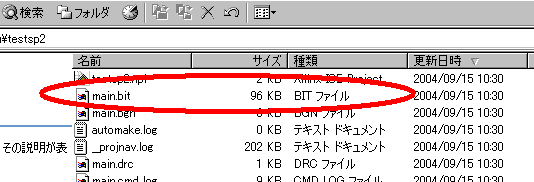

ISEやWebPACKでのコンパイルが終了すると、FPGAのデザイン一式があるフォルダに、BITファイルが生成されます。

MITOUJTAGでは、BITファイルをコンフィグROMに書込むことができるので、iMPACTを用いてMCSに変換する必要はありません。

これで、FPGA用データファイルの準備は完了です。

コンフィグROMにプログラミング

FPGA用のデータをコンフィグROMにプログラミングします。

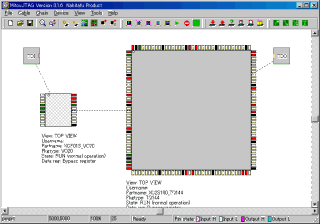

MITOUJTAGで、XCF01Sの絵の上にマウスカーソルを合わせ、左クリックをします。

XCF01Sの絵が灰色の網掛け(網掛けは選択されたことを表している)で表示されます。

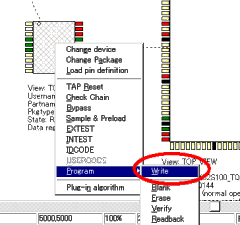

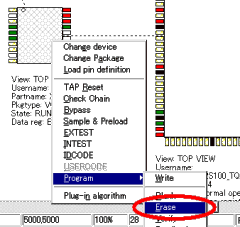

XCF01Sの絵の上で右クリックし、プルダウンメニューの中からProgram→Writeを選択するか、ツールバーの中の下向きの矢印のボタンを押します。

XCF01Sの絵の上で右クリックし、プルダウンメニューの中からProgram→Writeを選択するか、ツールバーの中の下向きの矢印のボタンを押します。

![]()

?

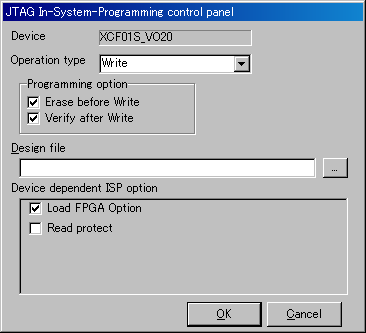

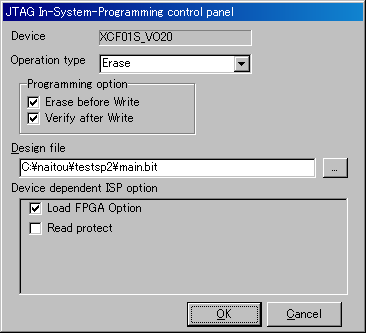

次の図のようなダイアログが表れるので、Design fileにISE FoundationやWebPACKで作成したBitファイル名を入力します。Design fileの右側にある[...]と書かれたボタンを押すと、ファイル参照ダイアログが開きます。

?

?

?

このダイアログでは、Load FPGA Optionというオプションがデフォルトでチェックされています。このオプションがチェックされていると、プログラミング終了後にコンフィグROMのCFピンからLのパルスを出力し、FPGAに再コンフィギュレーションを促します。

ROMのCFピンとFPGAのPROGピンが接続されている場合には、MITOUJTAGからFPGAの再コンフィギュレーションを意図的に行うことが可能です。

また、Read protectをチェックすると、コンフィグROMに書き込まれたデータがJTAG経由で読み出されるのを防ぐことができます。

?

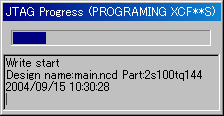

OKボタンを押すと、書込みが始まります。Erase→Write→Verifyの一連の流れは30秒くらいで終了します。

これで、FPGAのコンフィギュレーションは終了です。

誤ったデータを書いてしまった場合

もし、XC2S100を使っているのにXC2S30用のデータを書き込んでしまったり、Spartan3にSpartan2用のデータを書き込んでしまった場合は、FPGAは異常な動作をします。また、JTAGが使用できなくなることもあります。

そんなときでも慌てずに、下記の方法でコンフィグROMのデータを消去してください。

まず、下の図の画面に戻ってください。JTAGが使えなくなっているので、デバイスの自動認識ができないかもしれませんので、その時は手動でデバイスを追加します。

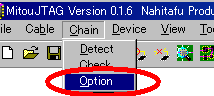

メインメニューで「Chain→Option」を選択します。

「Chain Option」ダイアログが開くので、Ignore ERRORをチェックしてOKボタンを押します。

XCF01Sの絵の上で右クリックし、プルダウンメニューからProgram→Eraseを選択するか、ツールバーの![]() のボタンを押します。

のボタンを押します。

下の図のようなダイアログが表れるので、OKボタンを押します。

これで、異常なデータが書かれたコンフィグROMが消去されるので、再度正しいデータを書き込んでください。

なお、FPGAのJTAGが正しく動作している場合は、Chain OptionでIgnore ERRORを設定する必要はありません。

バウンダリスキャン

バウンダリスキャンを用いると、デバイスの動作に影響を与えることなく、デバイスの動作を観察することができます。

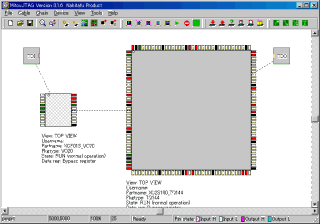

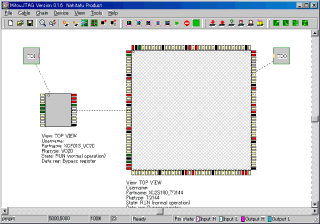

まず、上の図の画面で、右側のデバイス(XC2S100TQ144)の絵の上にマウスカーソルを合わせ、左クリックします。すると、次の図のように、右側のデバイスが灰色の網掛けで表示されます。

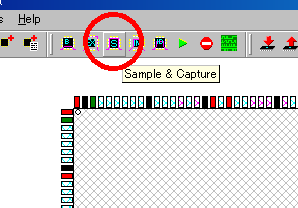

ツールバーの「S」と書かれたボタンを押します。すると、選択されたデバイスの各ピンの状態をサンプリングして、ピンの状態を画面上に色で表示します。

赤いピンはVCC、黒いピンはGNDです。

ピンクのピンはHを出力、水色のピンはLを出力しているピンです。ピンクの網掛けのピンはHを入力、水色の網掛けのピンはLを入力しているピンです。

このように、ピンの色と網掛けの状態で、どのような信号を入出力しているかが一目でわかります。

?

また、ツールバーの![]() のボタンを押すと、ピンの状態を連続してサンプリングして表示します。FPGAの動作が目に見えるようにわかるでしょう。

のボタンを押すと、ピンの状態を連続してサンプリングして表示します。FPGAの動作が目に見えるようにわかるでしょう。

?

連続サンプリングを止めるには、![]() のボタンを押します。

のボタンを押します。

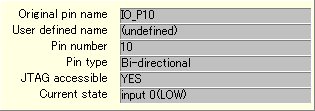

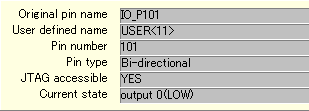

なお、ピンの絵の上にマウスカーソルを合わせ、右クリックすると、下の図のようなダイアログが表示されて、ピンの詳しい状態が表示されます。

ピンの名前の設定

XILINXのISEやWebPACKでコンパイルする時に、UCFファイルというものを使用します。UCFファイルにはピンの名前とピンの番号の対応付けが記述されています。MITOUJTAGではUCFファイルを読み込むことができます。

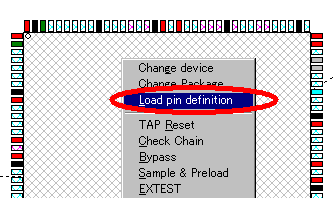

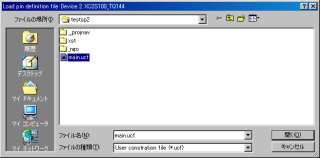

XC2S100TQ144の絵の上にマウスカーソルを合わせ、右クリックでプルダウンメニューを出します。Load pin definitionを選択します。

ファイル参照ダイアログが開くので、ISEで使用したUCFファイルを指定します。

これで、MITOUJTAGのピン名の定義が読み込まれました。

UCFを読み込んでおくと、次のロジックアナライザも便利に使用できます。

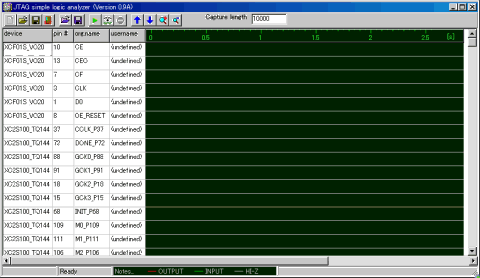

ロジックアナライザ

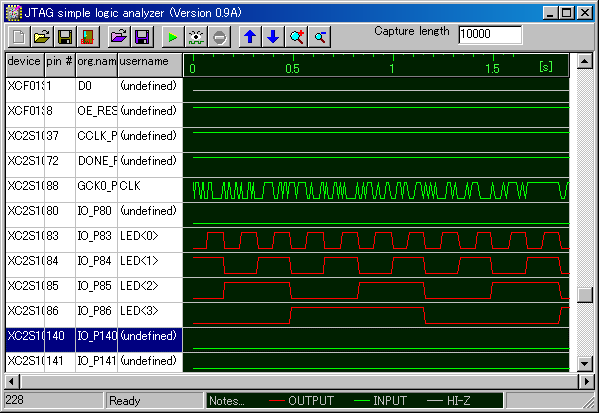

最後に、JTAGロジックアナライザの使い方を簡単に説明します。

JTAGロジックアナライザを起動するには、メインメニューから「Tools→Simple logic analyzer」を起動するか、 ツールバーの![]() ボタンを押します。

ボタンを押します。

JTAGロジックアナライザが起動したら、![]() のボタンを押せば波形をリアルタイムに表示します。

のボタンを押せば波形をリアルタイムに表示します。

![]() のボタンを押すとリアルタイムではありませんが、最高速度での取り込みが開始します。

のボタンを押すとリアルタイムではありませんが、最高速度での取り込みが開始します。

![]() ボタンを押すと、波形の取り込みやリアルタイムの波形観察を停止します。

ボタンを押すと、波形の取り込みやリアルタイムの波形観察を停止します。